# ACS APPLIED MATERIALS & INTERFACES

# Surface Engineering of Reduced Graphene Oxide for Controllable Ambipolar Flash Memories

Su-Ting Han,<sup>†</sup> Ye Zhou,<sup>†</sup> Prashant Sonar,<sup>\*,‡</sup> Huaixin Wei,<sup>†</sup> Li Zhou,<sup>†</sup> Yan Yan,<sup>†</sup> Chun-Sing Lee,<sup>†</sup> and V. A. L. Roy<sup>\*,†,§</sup>

<sup>†</sup>Department of Physics and Materials Science and Center of Super-Diamond and Advanced Films (COSDAF), City University of Hong Kong, Tat Chee Avenue, Kowloon, Hong Kong SAR

<sup>‡</sup>School of Chemistry, Physics and Mechanical Engineering, Queensland University of Technology (QUT), GPO Box 2434, Brisbane, QLD 4001, Australia

<sup>§</sup>Shenzhen Research Institute, City University of Hong Kong, High-Tech Zone, Nanshan District, Shenzhen, 518057, China

## **Supporting Information**

**ABSTRACT:** Tunable charge-trapping behaviors including unipolar charge trapping of one type of charge carrier and ambipolar trapping of both electrons and holes in a complementary manner is highly desirable for low power consumption multibit flash memory design. Here, we adopt a strategy of tuning the Fermi level of reduced graphene oxide (rGO) through self-assembled monolayer (SAM) functionalization and form p-type and n-type doped rGO with a wide range of manipulation on work function. The functionalized rGO can act as charge-trapping layer in ambipolar flash memories, and a dramatic transition of charging behavior from

unipolar trapping of electrons to ambipolar trapping and eventually to unipolar trapping of holes was achieved. Adjustable hole/ electron injection barriers induce controllable  $V_{\rm th}$  shift in the memory transistor after programming operation. Finally, we transfer the ambipolar memory on flexible substrates and study their charge-trapping properties at various bending cycles. The SAMfunctionalized rGO can be a promising candidate for next-generation nonvolatile memories.

KEYWORDS: self-assembled monolayer, reduced graphene oxide, work function, flash memory, ambipolar, charge-trapping behavior

# INTRODUCTION

Charge-trapping behavior including unipolar trapping of either electrons or holes as well as ambipolar trapping of both electrons and holes is one of the most important figures of merit for flash memories.<sup>1-4</sup> In nonvolatile floating gate-based memories, the charge carriers can be stored in the charge-trapping elements after programming operation and erased back to the semiconducting channel by reverse gate bias.<sup>5–9</sup> Threshold voltage  $(V_{\rm th})$  can be manipulated since the channel conductance depends on whether the charge carriers are stored in the floating gate or not.<sup>10,11</sup> The charge-trapping types can be justified by the shifting direction of the transfer curve. Employing unipolar charge trapping of either electrons or holes in a complementary manner is highly desirable for low power consumption, while the ambipolar trapping is an efficient approach for designing multilevel data storage memories.<sup>3</sup> In another aspect, ambipolar semiconducting materials have received a lot of interest for mimicking traditional complementary circuits.12-17 The complexity of the printed logic circuits design could be further reduced by using low band gap ambipolar materials and symmetric electrodes. In addition, investigating the ambipolar material based nonvolatile memories is necessary for the development of ambipolar integrated circuits with unique properties, which may not be achievable with unipolar semiconductors. On this regard, systematic control over the trapping behavior of ambipolar flash memory is critical for various practical applications. It is commonly believed that the charge-trapping behavior of flash memory is governed by the holes or electrons injection from the highest occupied molecular orbital (HOMO) or lowest unoccupied molecular orbital (LUMO) of semiconductor materials to the Fermi level of charge-trapping elements.<sup>3,18</sup> Tuning the Fermi level of the charge-trapping layer/floating gate in memory transistors can control the hole/electron trapping behaviors. However, because of the fixed Fermi level of metal nanoparticles in the nanofloating gate memory transistor, it is hard to achieve tunable electrical characteristics by manipulating the energy level.<sup>19,20</sup> Therefore, graphene can be a better choice for the charge-trapping layer since its Fermi level can be manipulated.<sup>21,22</sup> Previously, several methods including deposition of conjugated organic molecules,<sup>23</sup> using the Au-ion treatment<sup>21</sup> or ion irradiation,<sup>24</sup> have been introduced to tune the work function of graphene.

Received: October 21, 2014 Accepted: December 24, 2014 Published: December 24, 2014

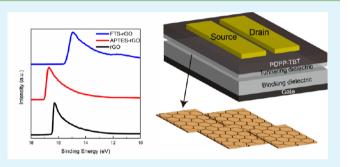

Figure 1. Tapping-mode AFM height image of (a) fabricated rGO film, (b) APTES-functionalized rGO, and (c) FTS-functionalized rGO. (d) The XPS data of pristine rGO and SAM-functionalized rGO. (e) UPS spectra of pristine rGO and SAM-functionalized rGO.

Nevertheless, these approaches cannot offer wide-range tuning of the graphene doping level from p-type to n-type. For this reason, alkylsilane with electron-withdrawing or electron-donating groups self-assembled on the graphene is proposed to introduce p-type/n-type doping of graphene with a wide range of manipulation of Fermi level.<sup>25,26</sup> In another aspect, traditional Si-based flash memories usually employ polycrystalline silicon as floating gate or Si<sub>3</sub>N<sub>4</sub> as charge-trapping layer. The work function of polycrystalline silicon can be tuned by different doping concentration,<sup>27</sup> and the charge-trapping behavior can also be adjusted by tailoring the composition of Si<sub>3</sub>N<sub>4</sub> layer.<sup>28</sup> However, these materials are always applied on the rigid substrate, which is not compatible with flexible electronics. Reduced graphene oxide (rGO) and its derivatives can be synthesized through a cheap solution-processed method, which is also highly transparent. These advantages make rGO more suitable to apply in the flexible flash memory with tunable charge-trapping behavior. Recently, some works reported on graphene and its derivativesbased flash memories;<sup>29</sup> however, few of them utilized rGO with tunable work functions to manipulate the charge-trapping behavior of the flash memories.

Herein, we present a simple approach to systematically modulate the trapping behavior of polymer ambipolar flash memory by utilizing alkylsilane self-assembled monolayer (SAM) functionalized rGO as charge-trapping layer. The ambipolar polymer material, poly(diketopyrrolopyrrolethiophenebenzothiadiazolethiophene) (PDPP-TBT) is employed as active layer. Two kinds of alkylsilane compounds, namely, (tridecafluoro-1,1,2,2,-tetrahydrooctyl) trichlorosilane (FTS) with electron-withdrawing group and aminopropyl triethoxysilane (APTES) with electron-donating group are selected to introduce p-type and n-type doping of the rGO layer, respectively. The systematic shifts of the Fermi level of rGO induces a dramatic transition of the charging behavior from unipolar trapping of electrons to ambipolar trapping and eventually to unipolar trapping of holes. The doping process of rGO was investigated by X-ray photoemission spectroscopy (XPS). Ultraviolet photoemission spectroscopy (UPS) was used to characterize the work function of rGO after SAM doping. The narrowed holes/electrons injection barrier originated from the Fermi level shifts of functionalized rGO layer have strong contribution to the ambipolar/unipolar charging behavior alteration when considering the HOMO/LUMO level of PDPP-TBT. Our device fabrication techniques, including synthesis of rGO sheets, formation of rGO layers, and alkylsilane self-assembled onto the rGO layers, are all based on lowtemperature solution-processed method, and we have also demonstrated the ambipolar memory transistor on flexible substrates to achieve low-voltage operation.

## RESULTS AND DISCUSSION

The fabricated rGO film contains a few layers of rGO sheets. The precleaned SiO<sub>2</sub>/Si substrate is fully covered by rGO sheets through simply spin-casting the rGO solution with an average rGO sheet size of 200 nm. Utilization of alkylsilane molecules to form SAM functionalization on the rGO film was obtained through dipping process, while the SAM reagents were coupled to the rGO surface directly. The atomic force microscopy (AFM) images indicating the effect of APTES and FTS SAMs on the morphology of rGO layer are illustarted in Figure 1a–c. The thickness of rGO film is ~5 nm. The small bumps nucleated due to SAM functionalization can be observed. The X-ray photoelectron spectroscopy (XPS) was utilized to investigate the growth of SAMs on rGO surface. As shown in Figure 1d, the XPS

## **ACS Applied Materials & Interfaces**

spectrum of pristine rGO exhibits four peaks at 530, 284, 157, and 106 eV, which correspond to  $O_{1s}$ ,  $C_{1s}$ ,  $Si_{2s}$ ,  $Si_{2p}$ , respectively.<sup>30</sup> The existence of numerous oxygen-containing functional groups on rGO plays a significant role for the covalent bonding of FTS and APTES with rGO.<sup>31</sup> APTES molecules can graft onto the rGO surface (APTES-rGO) by its amino group reacting with the epoxy group of rGO.<sup>32</sup> It is reasonable that the  $N_{1,s}$  signal at 400 eV is relatively small since there are fewer epoxy groups than hydroxyl groups on rGO.<sup>26</sup> However, the hydroxyl groups can act as nucleation sites to prompt the assembly of FTS on rGO.33 The peaks observed at 862, 835, and 689 eV correspond to F (KLL) and F<sub>1s</sub> in the XPS spectrum of FTSfunctionalized rGO (FTS-rGO). The nitrogen and fluorine signal of APTES-rGO and FTS-rGO demonstrate successful covalent doping of rGO films with APTES and FTS. XPS C 1s spectra of pristine rGO, APTES-rGO, and FTS-rGO are shown in Supporting Information (Figure S1). C-N signal can be observed in APTES-rGO, indicating that the amino moieties react with the epoxy groups on rGO surface.  $C-CF_2$  and  $O-CF_2$ signal can be found in the FTS-rGO, demonstrating the successful functionaliztion.<sup>34</sup> The energy spectra of SAMs functionalization of rGO were further investigated by ultraviolet photoelectron spectroscopy (UPS) as depicted in Figure 1e. A gold plate was used for the calibration in the experiment. The vacuum level of the tested samples was determined by linear extrapolation of secondary electron cutoffs on the high-binding energy side of the UPS spectra (14-18 eV).<sup>35</sup> The work function (WF) was calculated by subtracting  $E_{SE}$  from  $h\nu$ , where  $E_{SE}$  and  $h\nu$  are the secondary edge position and the incident photon energy (21.2 eV).<sup>36</sup> The WF of rGO is calculated to be  $\sim 4.74$  eV, which is consistent with the reported value of chemically rGO.37,38 Compared with the pristine rGO, the APTES-rGO sample displays n-doped property with the decreased WF of 4.21 eV, while the FTS-rGO sample is intensely p-doped with the increased WF of 5.70 eV. The WFs of the SAM-functionalized rGO samples vary more widely compared with Au ion-doped rGOs (increase the WF from 4.4 to 5.0 eV<sup>39</sup>), suggesting that direct surface engineering of rGO can induce efficient doping. Previous reports show that the carrier concentration of rGO varies with the SAM functionalization and that the doping of rGO leads to the tunable work function.<sup>26</sup> The upward shift of Fermi level of APTES-rGO is mainly attributed to the electrondonating group of APTES molecules, electrostatic potential created by the dipole moment of APTES, while the electronwithdrawing characteristics of FTS and protonic doping via unreacted silanol groups induce the increased WF of FTSrGO.<sup>39-41</sup>

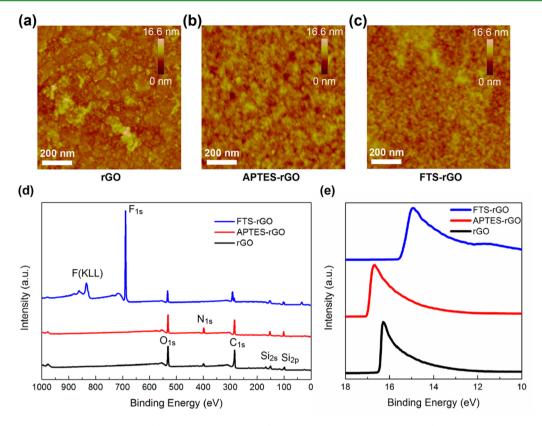

Figure 2a shows an illustration of the three-dimensional (3D) structure for bottom-gate top-contact ambipolar flash memory devices and the chemical structure of the ambipolar materials PDPP-TBT and alkysilanes (APTES and FTS). Silicon wafers with 300 nm thick SiO<sub>2</sub> layers serve as the gate electrodes and blocking dielectric layers. After spin-coating the rGO films, the substrates were then immersed into the APTES and FTS solutions to form the monolayers. Then another 5 nm atomic layer deposited (ALD) aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) was deposited as tunneling dielectric layer to prevent charge leakage from the doped rGO layer to the semiconductor layer as well as to decrease the electrostatic force from SAMs layers, which may affect the charge transport in semiconductor layer. It is worth noting that the Al<sub>2</sub>O<sub>3</sub> deposition was performed at 80 °C. The thermal stability of work function value can be well-maintained at the temperature lower than 800 °C.<sup>42</sup> In another aspect, the FTS

**Figure 2.** (a) Three-dimensional schematic illustration of the ambipolar memory device, chemical structure of PDPP-TBT, and the used alkysilane in the experiment: aminopropyl triethoxysilane (APTES) and (tridecafluoro-1,1,2,2,-tetrahydrooctyl) trichlorosilane (FTS). (b) Energy band diagrams of SAM-doped rGO and the semiconducting polymer PDPP-TBT.

and APTES are covalently bonded to rGO, which is also stable at 80 °C. The scanning electron microscope (SEM) images of the APTES-rGO and FTS-rGO films are shown in Supporting Information (Figures S2 and S3). Finally, the ambipolar PDPP-TBT was spin-coated as an active layer followed by the thermal evaporation of 40 nm of Au as source/drain electrodes. The synthesis procedure of PDPP-TBT can be found in the literature.<sup>13</sup> Figure 2b represents the schematic diagram of energy levels of the SAM-doped rGO and ambipolar polymer in the memory transistors, where the  $\Phi_e$  and  $\Phi_h$  are barrier heights of carrier injection at the interface for electrons and holes, respectively.

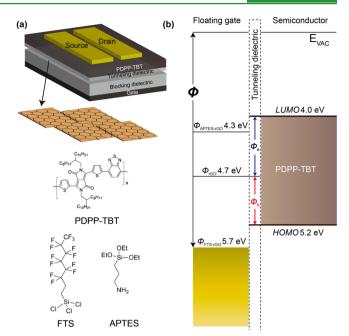

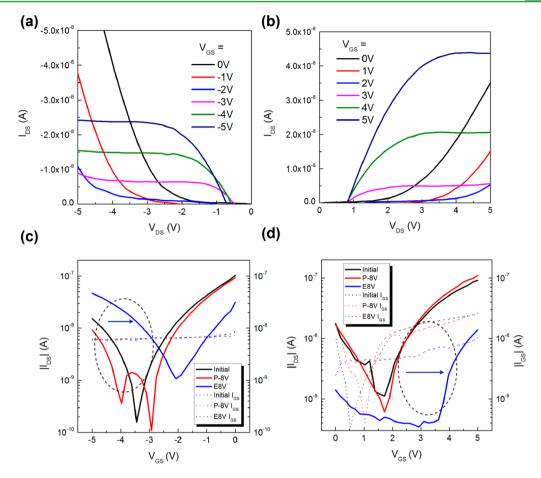

Figure 3a,b shows the typical output characteristics of the fabricated ambipolar field-effect transistors (FET) at holeenhancement type and electron-enhancement type, respectively. The devices without embedding the rGO sheets (device structure: Si/300 nm SiO<sub>2</sub>/5 nm Al<sub>2</sub>O<sub>3</sub>/PDPP-TBT/Au source-drain) were fabricated as control devices to determine the charging effects in the transistor structure. Unless otherwise mentioned, all the device structures and the processing conditions are the same compared with the ambipolar memory devices except the insertion of rGO layers. The transistors are operated in both hole-enhancement mode and electronenhancement mode. The drain-source current  $I_{DS}$  increases exponentially with increasing drain-source voltages  $(V_{DS})$  at relative low gate-source voltages ( $V_{GS}$ ). Figure 3c,d shows the transfer curves of initial states and different programmed states  $(\pm 90 \text{ V})$  in p-type operation and n-type operation, respectively. Hole-enhancement mode can be observed at  $V_{GS} < -26.3$  V with  $V_{\rm DS}$  of -50 V, while electron-enhancement mode is obtained at  $V_{\rm GS} > 20.6$  V at  $V_{\rm DS} = 50$  V. The electron and hole mobilities at the saturation regime are  $1 \times 10^{-2}$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and  $2 \times 10^{-4}$  cm<sup>2</sup>  $V^{-1}$  s<sup>-1</sup>, respectively. A negligible memory window was observed after applying bias pulses of  $\pm 90$  V for 1 s in either hole-

Figure 3. Initial output characteristics of the ambipolar transistor at (a) hole-enhancement mode and (b) electron-enhancement mode. Transfer curves of the ambipolar transistor before and after programming at  $\pm 90$  V for 1 s at (c) p-type enhancement mode and (d) n-type enhancement mode.

enhancement or electron-enhancement mode, implying almost no charging/discharging effect occurred for the charge carriers in the bulk or at the interfaces of the gate dielectric layer.

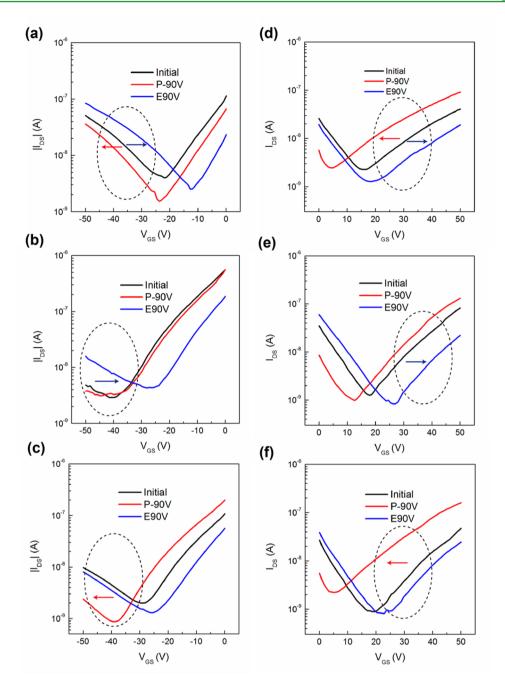

Subsequently, the charge-trapping behavior of ambipolar memory devices was studied. The transfer characteristics of the memory devices based on rGO (denoted as rGO device), APTES-rGO (denoted as APTES-rGO device), and FTS-rGO (denoted as FTS-rGO device) after different programming operations  $(\pm 90 \text{ V for } 1 \text{ s})$  at the p-type enhancement mode and n-type enhancement mode are shown in Figure 4. Almost no decrease in the charge mobility of the ambipolar polymer was observed after embedding pristine rGO and SAM-doped rGO in Al<sub>2</sub>O<sub>3</sub> layer, which is satisfactory enough to ensure efficient operation. The  $V_{\rm th}$  value varied in the initial state after inserting the pristine rGO and SAM-functionalized rGO compared with standard FET device. The V<sub>th</sub> shifts are originated from presence of traps and relatively rough interface introduced by rGO chargetrapping layers. The  $V_{\rm th}$  of initial state (denote as  $V_{\rm th}$  (initial)),  $V_{\rm th}$  of negative programmed state (denoted as  $V_{\rm th}$  (negative programmed)), and  $V_{\rm th}$  of positive programmed state (denoted as  $V_{\rm th}$  (positive programmed)) of all the devices are summarized in Table 1. For rGO device, after the application of negative bias in gate electrode,  $V_{\rm th}$  is shifted toward the negative direction, and after applying positive bias,  $V_{\rm th}$  is shifted toward the positive direction at both p-type enhancement mode and n-type

enhancement mode. The negatively shifted V<sub>th</sub> shows that more and more holes are trapped in the process, and the potential evolved from these traps screens the gate voltage after applying -90 V at the gate, while the stored holes are compensated by electrons; electrons are eventually trapped in the rGO layer due to the additional positive bias of +90 V. It can be seen that both electrons and holes participate in the chargetrapping process in the rGO device during the programming operation.<sup>3</sup> Well-balanced V<sub>th</sub> shifts obtained after negative and positive programming operations reveal ambipolar trapping capability of rGO device. In contrast to ambipolar trapping observed in rGO device, hole-trapping of APTES-rGO device could not be evaluated because  $V_{\rm th}$  shift was negligible after applying negative bias in gate electrode, while electron-trapping of FTS-rGO device was difficult to achieve since  $V_{\rm th}$  shift was insignificant after positive programming operation. More than 10 devices have been measured, and similar electrical characteristics can be observed. Direct tunneling (at relatively low voltage) and Fowler–Nordheim (F–N) tunneling (at relatively high voltage) are considered as the favorable routes in program/erase operations rather than the channel hot hole/electron injection due to the low drift velocity of charge carriers in ambipolar polymer.<sup>43,44</sup> In the programming operation, the electrical field across the tunneling dielectric layer could be calculated by the following equation

Research Article

**Figure 4.** Electrical characteristics of ambipolar memory transistors based on (a) undoped rGO, (b) APTES-functionalized rGO, and (c) FTS-functionalized rGO at hole-enhancement mode. Electrical characteristics of ambipolar memory transistors based on (d) undoped rGO, (e) APTES-functionalized rGO, and (f) FTS-functionalized rGO at electron-enhancement mode.

| Table 1. Measured V | L of initial states. | programmed states at | different operation modes |

|---------------------|----------------------|----------------------|---------------------------|

|                     |                      |                      |                           |

|                        |                           | hole-enhancement mode                 |                                       |                                                      | electron-enhancement mode             |                                       |  |

|------------------------|---------------------------|---------------------------------------|---------------------------------------|------------------------------------------------------|---------------------------------------|---------------------------------------|--|

|                        | $V_{ m th}$ (initial) [V] | $V_{ m th}$ (negative programmed) [V] | $V_{ m th}$ (positive programmed) [V] | $V_{\mathrm{th}} (\mathrm{initial}) \\ [\mathrm{V}]$ | $V_{ m th}$ (negative programmed) [V] | $V_{ m th}$ (positive programmed) [V] |  |

| rGO                    | -18                       | -25                                   | -12                                   | 15                                                   | 5                                     | 26                                    |  |

| APTES-rGO              | -15                       | -16                                   | 0.5                                   | 25.5                                                 | 23.5                                  | 37                                    |  |

| FTS-rGO                | -20                       | -35                                   | -19                                   | 24                                                   | 7                                     | 27                                    |  |

| flexible APTES-<br>rGO | -3                        | -3.4                                  | -1.4                                  | 1.4                                                  | 1.3                                   | 3.2                                   |  |

$$E_{1} = \frac{V_{\rm GS}}{d_{1} + d_{2}(\varepsilon_{1}/\varepsilon_{2})} + \frac{Q}{\varepsilon_{1} + \varepsilon_{2}(d_{1}/d_{2})}$$

(1)

where  $\varepsilon_i$  are the dielectric constants,  $d_i$  is the thickness of the two dielectric layers, and Q is the stored charge carrier on the rGO layers. At the initial stage of the ambipolar memory device

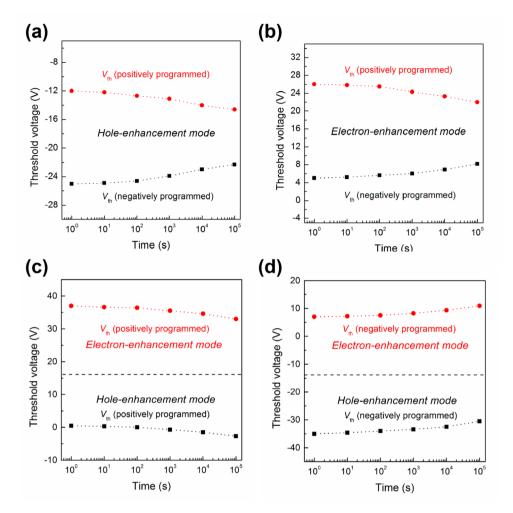

Figure 5. Retention properties of (a, b) rGO device, (c) APTES-rGO device, and (d) FTS-rGO device at different operation modes.

operation (Q = 0 and  $V_{GS} = \pm 90$  V), the electrical field in the Al<sub>2</sub>O<sub>3</sub> tunneling dielectric layers for these three devices is estimated to be 1.78 MV/cm<sup>2</sup>. In general, high electrical field in the tunneling dielectric layer would promote an efficient injection of both holes and electrons from the ambipolar semiconductor to the charge-trapping layer and trapping in charge-trapping layer, however, which is inconsistent with unbalanced charge trapping observed in the APTES-rGO device and FTS-rGO device. These results show that the chargetrapping behavior varies with the SAM functionalization. In the rGO-based memory transistors, the charge carriers can be stored in the Fermi level of rGO domains surrounded by the band gap of tunneling and blocking dielectrics. Considering similar applied electrical fields of these three devices, the distinctive chargetrapping behaviors are mainly attributed to the difference of energy levels since the programming operation is inversely proportional to the injection barrier arising from the Fermi level of the floating gate and HOMO/LUMO levels of semiconductor layer.<sup>3,18</sup> Fermi level of pristine rGO is centered between the HOMO level and LUMO level of PDPP-TBT with the hole injection barrier of 0.5 eV and electron injection barrier of 0.7 eV, suggesting a comparable tunneling rate of holes and electrons. The easier positive programming process and harder negative programming process of APTES-rGO device can be explained by the narrowed electron injection barrier of 0.3 eV and extended hole injection barrier of 0.9 eV, which are induced by up-shifting Fermi level of APTES-rGO. Similarly, the reason for the unipolar

trapping of holes observed in FTS-rGO device is due to the huge electron injection barrier height of 1.7 eV, which originates from the strong p-doping of FTS-rGO. The cumulative  $V_{\rm th}$  shifts as a function of bias time are shown in Supporting Information (Figure S4).  $V_{\rm th}$  shift increases with the increased programming/ erasing operation time. The plot of the memory windows versus various gate voltages is shown in Supporting Information (Figure S5). We increased the programming/erasing (*P/E*) voltages from  $\pm 70$  V to  $\pm 90$  V for the ambipolar memory devices. In general, enhancing the *P/E* voltage will increase the probability of tunneling events and therefore increase the number of trapped/detrapped charge carriers.

It is imperative that the retention time should be sufficient for long-term stable data storage. Figure 5 shows retention characteristics of rGO device, APTES-rGO device, and FTSrGO device in the hole-enhancement and electron-enhancement mode, respectively. The stored data has an estimated retention time of as high as ~10<sup>5</sup> s, which is comparable to other types of flash memory devices. Vertical loss of the stored charges may usually originate from the charge-carrier diffusion from the rGO sheets through the tunneling Al<sub>2</sub>O<sub>3</sub> layer. In our designed system, the rGO/Al<sub>2</sub>O<sub>3</sub> structure offers a large barrier height to maintain the trapped holes/electrons in rGO. The retention property of the ambipolar memory at high temperature (80 °C) is also investigated and shown in the Supporting Information (Figure S6). The data retention ability is sensitive to the temperature, and it reduces with increased temperature due to thermal excitation

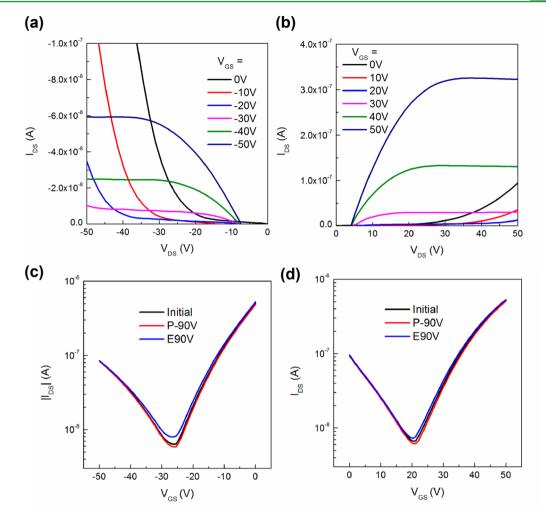

Figure 6. Output characteristics of the flexible memory device based on APTES-rGO at (a) hole-enhancement mode and (b) electron-enhancement mode. Transfer curves of the flexible memory device before and after programming the gate ( $\pm 8$  V for 1 s) at (c) hole-enhancement mode and (d) electron-enhancement mode.

of trapped charge carriers.<sup>45</sup> The large available thermal energy at higher temperature induces inferior quantum confinement effects and increases the possibility of charge loss over time.

The tunable charge-trapping properties of the ambipolar memory based on SAM-functionalized rGO has been further extended to flexible substrates toward the realization of nextgeneration soft electronics. We fabricated flexible memory transistors based on APTES-rGO with low-voltage operation. A 25 nm thick silver (Ag) gate electrode was deposited on the (polyethylene terephthalate) substrate as gate electrode. A 15 nm thick aluminum oxide  $Al_2O_3$  (blocking dielectric layer) and 5 nm thick Al<sub>2</sub>O<sub>3</sub> (tunneling dielectric layer) were atomic layer deposited, and the APTES-rGO charge-trapping layer was inserted between them. The typical output curves of the flexible ambipolar memory devices based on APTES-rGO under lowvoltage operations are shown in Figure 6a,b. The saturation of the  $I_{\rm DS}$  is observed at both high positive and negative  $V_{\rm GS}$  values, indicating electrons and holes are accumulated at the respective  $V_{\rm GS}$ . At low  $V_{\rm GS}$ , the transistors show diode-like curves with a rapid increase of  $I_{DS}$  with  $V_{DS}$ , which can be attributed to the presence of both charge carriers in the channel. The memory characteristics were further examined by measuring the  $V_{\rm th}$  shift with respect to different programming operations ( $\pm 8$  V for 1 s). Figure 6c,d displays the transfer curves in hole-enhancement and electron-enhancement mode, respectively. The  $V_{\rm th}$  (initial),  $V_{\rm th}$ (negative programmed), and  $V_{\rm th}$  (positive programmed) of flexible APTES-rGO device are -3, -3.4, and -1.4 V in p-type

operation and 1.4, 1.3, and 3.2 V in n-type operation. A negligible memory window after the negative programming opeartion and large  $V_{\rm th}$  shift after the positive programmed operation imply uniploar trapping of electrons, which is in good agreement with the performance of high-voltage operated APTES-rGO device on the rigid substrate. The relatively large gate current can be eliminated by the further modification of tunneling dielectric layer.

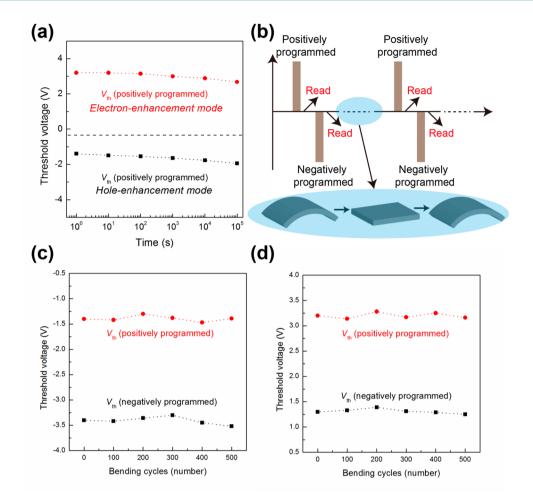

Figure 7a displays retention characteristics for flexible APTESrGO device. The  $V_{\rm th}$  (positively programmed) values at both hole-enhancement and electron-enhancement modes could be maintained for more than 10<sup>5</sup> s. Furthermore, we examined the  $V_{\rm th}$  of negatively programmed and positively programmed states under a bending radius of curvature of 1 cm (tensile and compressive strain of  $\pm 1\%$ ) as shown in Figure 7b. The flexible memory transistors based on APTES-rGO at both holeenhancement and electron-enhancement modes did not exhibit obvious degradation of  $V_{\rm th}$  after 500 bending cycles as demonstarted in Figure 7c,d. During the bending test, our flexible memory transistors exhibit excellent mechanical properties, demonstrating the potential application in flexible integrated circuits. Another important reliability test for nonvolatile memory devices is endurance performance.<sup>29,46,47</sup> The endurance properties of the flexible ambipolar memory device are shown in Supporting Information, Figure S7. These data states of the memory devices were well-maintained, and the whole data level range did not degrade for over 500 P/E cycles.

Figure 7. (a) Retention properties of flexible ambipolar flash memory based on APTES-rGO. (b) Illustration of the bending tests. Mechanical stability tests of flexible ambipolar flash memory at (c) hole-enhancement mode and (d) electron-enhancement mode.

#### CONCLUSION

In summary, the SAM-doped rGO is first utilized as chargetrapping element in ambipolar flash memory. Upward and downward shifting of the Fermi level of rGO were achieved via direct surface functionalization using APTES and FTS SAMs, respectively. The UPS results evidence that the work functions vary in a wide range from 4.3 to 5.7 eV, which is superior to the conventional chemically doped rGO. After inserting the doped and undoped rGO between the blocking and tunneling dielectric layers, a transition from ambipolar trapping of both holes and electrons in rGO device to unipolar trapping of electrons/holes in APTES-rGO/FTS-rGO devices occurred. The energy level alignment plays a critical role in the device performance. The adjustable hole/electron injection barriers induce the significant  $V_{\rm th}$  shift after positive/negative programming operation and negligible  $V_{\rm th}$  shift after application of negative/positive gate bias. The unipolar electron-trapping properties of flash memory based on APTES-rGO were further demonstrated on the flexible substrate. It is believed that SAM-doped rGO-based ambipolar memory cells can bring the development of polymer nonvolatile memory device a step closer to functional applications in nextgeneration flexible electronics.

## METHODS

**Preparation of rGO and SAM Functionalization.** Graphite oxide was synthesized using Hummer's method. Graphite oxide (12.5 mg) was

then suspended in 25 mL of deionized water to form brown dispersion. Ultrasonication was taken for 1 d to exfoliate the graphite oxide into graphene oxide (GO). Hydrazine monohydrate (10  $\mu$ L) was added to the homogeneous yellow-brown 10 mg mL<sup>-1</sup> GO solution in a mixture of *N*,*N*-dimethylformamide (DMF) and water in a volume ratio of 9:1, and the solution was heated with vigorous stirring at 80 °C for 12 h. A small amount of poly(vinyl alcohol) (weight ratio of GO/PVA is 10:1) was used as an additive to prevent the agglomeration of the well-dispersed rGO solution. A homogeneous colloidal suspension of RGO was spin-cast onto Si wafers. The substrates were then transferred to SAM reactors. FTS was reacted with the surface of the rGO film in anhydrous *n*-hexane solvent for 2 min, and APTES was reacted in anhydrous toluene solvent (20 mL) for 90 min to compensate for its low reactivity. The concentration of FTS and APTES in the organic solution is 25  $\mu$ L/10 mL.

**Device Fabrication.** Ambipolar memory transistors were fabricated on heavily n-doped Si wafers with 300 nm of SiO<sub>2</sub> as gate dielectric layer. Low-voltage flexible memory transistors were fabricated on 200  $\mu$ m thick PET substrate with 15 nm of Al<sub>2</sub>O<sub>3</sub>. The PDPP-TBT films were formed on the substrates by spin-coating from 7 mg mL<sup>-1</sup> PDPP-TBT in chloroform solution, and thermal annealing at 160 °C for 30 min was then carried out in nitrogen glovebox. The Al<sub>2</sub>O<sub>3</sub> tunneling and blocking layers were deposited using a Savannah 100 ALD system, while the substrate temperature was kept at 80 °C. Patterned 40 nm gold electrodes with a channel length of 50  $\mu$ m and width of 1000  $\mu$ m were thermally evaporated through a shadow mask under 3 × 10<sup>-6</sup> Torr base pressure.

**Characterization.** The thicknesses of layers  $(SiO_2, Al_2O_3, and PDPP-TBT)$  were checked with the ellipsometer. The morphologies of

#### **ACS Applied Materials & Interfaces**

SAM-functionalized rGO were examined by AFM (Veeco Multimode V). The photoemission measurements were performed in a VGESCALAB 220i-XL UHV surface analysis system with a base vacuum of  $1 \times 10^{-10}$  Torr. The tested samples were prepared on the precleaned silicon substrate and then transferred into the chamber. A monochromatic Al K $\alpha$  X-ray source (1486.6 eV) was adopted to investigate the possible interfacial chemical reactions and changes of energy level when doing the XPS measurement. A He discharge lamp (21.2 eV) with 90 meV instrumental energy resolution as valued from the Fermi edge of a cleaned Au plate was used to measure the valence structure of the sample when doing the UPS measurement. All the samples were biased at -5 V with respect to ground for efficient collection of the secondary electrons. The electrical performances of the memory devices were characterized by a Keithley 2612 source meter in nitrogen glovebox at room temperature.

#### ASSOCIATED CONTENT

#### **Supporting Information**

C 1s XPS spectra and SEM images of the SAM-rGO, memory window with respect to various P/E time and voltage, retention property of the flexible device at 80 °C, and the P/E endurance characteristics of the flexible device. This material is available free of charge via the Internet at http://pubs.acs.org.

#### AUTHOR INFORMATION

#### **Corresponding Authors**

\*E-mail: val.roy@cityu.edu.hk. (V.A.L.R.) \*E-mail: sonar.prashant@qut.edu.au. (P.S.)

#### Notes

The authors declare no competing financial interest.

#### ACKNOWLEDGMENTS

We acknowledge grants from Shenzhen Municipality Project No. JCYJ20120618115445056, the Research Grants Council of the Hong Kong Special Administrative Region (Project No.T23-713/11), and City University of Hong Kong's Strategic Research Grant Project No. 7004012. P.S. is thankful to the ARC Future Fellowship Scheme (FT130101337) at Queensland University of Technology (QUT), Brisbane QLD.

### REFERENCES

(1) Zhou, Y.; Han, S.-T.; Xu, Z.-X.; Roy, V. A. L. Controlled Ambipolar Charge Transport Through a Self-Assembled Gold Nanoparticle Monolayer. *Adv. Mater.* **2012**, *24*, 1247–1251.

(2) Myung, S.; Park, J.; Lee, H.; Kim, K. S.; Hong, S. Ambipolar Memory Devices Based on Reduced Graphene Oxide and Nano-particles. *Adv. Mater.* **2010**, *22*, 2045–2049.

(3) Zhou, Y.; Han, S.-T.; Sonar, P.; Roy, V. A. L. Nonvolatile Multilevel Data Storage Memory Device from Controlled Ambipolar Charge Trapping Mechanism. *Sci. Rep.* **2013**, *3*, 2319.

(4) Baeg, K.-J.; Khim, D.; Kim, J.; Yang, B.-D.; Kang, M.; Jung, S.-W.; You, I.-K.; Kim, D.-Y.; Noh, Y.-Y. High-Performance Top-Gated Organic Field-Effect Transistor Memory using Electrets for Monolithic Printed Flexible NAND Flash Memory. *Adv. Funct. Mater.* **2012**, *22*, 2915–2926.

(5) Tseng, C. W.; Huang, D. C.; Tao, Y. T. Azobenzene-functionalized Gold Nanoparticles as Hybrid Double-Floating-Gate in Pentacene Thin-Film Transistors/Memories with Enhanced Response, Retention and Memory Windows. *ACS Appl. Mater. Interfaces* **2013**, *5*, 9528–9536.

(6) Lin, Y. W.; Lin, C. J.; Chou, Y. H.; Liu, C. L.; Chang, H. C.; Chen, W. C. Nonvolatile Organic Field Effect Transistor Memory Devices Using One-Dimensional Aligned Electrospun Nanofiber Channels of Semiconducting Polymers. J. Mater. Chem. C 2013, 1, 5336–5343.

(7) Chou, Y.-H.; Lee, W.-Y.; Chen, W.-C. Self-Assembled Nanowires of Organic n-Type Semiconductor for Nonvolatile Transistor Memory Devices. *Adv. Funct. Mater.* **2012**, *22*, 4352–4359.

(8) She, X.-J.; Liu, J.; Zhang, J.-Y.; Gao, X.; Wang, S.-D. Spatial Profile of Charge Storage in Organic Field-Effect Transistor Nonvolatile Memory Using Polymer Electret. *Appl. Phys. Lett.* **2013**, *103*, 143302.

(9) Lee, J.-S. Recent Progress in Gold Nanoparticle-Based Non-Volatile Memory Devices. *Gold Bull.* **2010**, *43*, 189–199.

(10) Zhou, Y.; Han, S.-T.; Chen, X.; Wang, F.; Tang, Y.-B.; Roy, V. A. L. An Upconverted Photonic Nonvolatile Memory. *Nat. Commun.* **2014**, *5*, 4720.

(11) Han, S.-T.; Zhou, Y.; Xu, Z.-X.; Roy, V. A. L. Controllable Threshold Voltage Shifts of Polymer Transistors and Inverters by Utilizing Gold Nanoparticles. *Appl. Phys. Lett.* **2012**, *101*, 033306.

(12) Díez-Pérez, I.; Li, Z.; Guo, S.; Madden, C.; Huang, H.; Che, Y.; Yang, X.; Zang, L.; Tao, N. Ambipolar Transport in an Electrochemically Gated Single-Molecule Field-Effect Transistor. *ACS Nano* **2012**, *6*, 7044–7052.

(13) Sonar, P.; Singh, S. P.; Li, Y.; Soh, M. S.; Dodabalapur, A. A Low-Bandgap Diketopyrrolopyrrole-Benzothiadiazole-Based Copolymer for High-Mobility Ambipolar Organic Thin-Film Transistors. *Adv. Mater.* **2010**, *22*, 5409–5413.

(14) Baeg, K.-J.; Caironi, M.; Noh, Y.-Y. Toward Printed Integrated Circuits based on Unipolar or Ambipolar Polymer Semiconductors. *Adv. Mater.* **2013**, *25*, 4210–4244.

(15) Bao, W.; Cai, X.; Kim, D.; Sridhara, K.; Fuhrer, M. S. High Mobility Ambipolar  $MoS_2$  Field-Effect Transistors: Substrate and Dielectric Effects. *Appl. Phys. Lett.* **2013**, *102*, 042104.

(16) Bisri, S. Z.; Gao, J.; Derenskyi, V.; Gomulya, W.; Iezhokin, I.; Gordiichuk, P.; Herrmann, A.; Loi, M. A. High Performance Ambipolar Field-Effect Transistor of Random Network Carbon Nanotubes. *Adv. Mater.* **2012**, *24*, 6147–6152.

(17) Liu, C.; Liu, Z.; Lemke, H. T.; Tsao, H. N.; Naber, R. C. G.; Li, Y.; Banger, K.; Müllen, K.; Nielsen, M. M.; Sirringhaus, H. High-Performance Solution-Deposited Ambipolar Organic Transistors Based on Terrylene Diimides. *Chem. Mater.* **2010**, *22*, 2120–2124.

(18) Hong, A. J.; Song, E. B.; Yu, H. S.; Allen, M. J.; Kim, J.; Fowler, J. D.; Wassei, J. K.; Park, Y.; Wang, Y.; Zou, J.; Kaner, R. B.; Weiller, B. H.; Wang, K. L. Graphene Flash Memory. *ACS Nano* **2011**, *5*, 7812–7817.

(19) Han, S.-T.; Zhou, Y.; Xu, Z.-X.; Roy, V. A. L.; Hung, T. F. Nanoparticle Size Dependent Threshold Voltage Shifts in Organic Memory Transistors. *J. Mater. Chem.* **2011**, *21*, 14575–14580.

(20) Lee, J.-S.; Cho, J.; Lee, C.; Kim, I.; Park, J.; Kim, Y.-M.; Shin, H.; Lee, J.; Caruso, F. Layer-by-Layer Assembled Charge-Trap Memory Devices with Adjustable Electronic Properties. *Nat. Nanotechnol.* **2007**, *2*, 790–795.

(21) Kwon, K. C.; Choi, K. S.; Kim, S. Y. Increased Work Function in Few-Layer Graphene Sheets via Metal Chloride Doping. *Adv. Funct. Mater.* **2012**, *22*, 4724–4731.

(22) Liu, J.; Lin, Z.; Liu, T.; Yin, Z.; Zhou, X.; Chen, S.; Xie, L.; Boey, F.; Zhang, H.; Huang, W. Multilayer Stacked Low-Temperature-Reduced Graphene Oxide Films: Preparation, Characterization, and Application in Polymer Memory Devices. *Small* **2010**, *6*, 1536–1542.

(23) Ishikawa, R.; Bando, M.; Morimoto, Y.; Sandhu, A. Doping Graphene Films *via* Chemically Mediated Charge Transfer. *Nanoscale Res. Lett.* **2011**, *6*, 1–5.

(24) Tapasztó, L.; Dobrik, G.; Nemes-Incze, P.; Vertesy, G.; Lambin, P.; Biró, L. P. Tuning the Electronic Structure of Graphene by Ion Irradiation. *Phys. Rev. B* **2008**, *78*, 233407.

(25) Park, J.; Lee, W. H.; Huh, S.; Sim, S. H.; Kim, S. B.; Cho, K.; Hong, B. H.; Kim, K. S. Work-Function Engineering of Graphene Electrodes by Self-Assembled Monolayers for High-Performance Organic Field-Effect Transistors. J. Phys. Chem. Lett. **2011**, *2*, 841–845.

(26) Kang, B.; Lim, S.; Lee, W. H.; Jo, S. B.; Cho, K. Work-Function-Tuned Reduced Graphene Oxide via Direct Surface Functionalization as Source/Drain Electrodes in Bottom-Contact Organic Transistors. *Adv. Mater.* **2013**, 25, 5856–5862.

(27) Sim, J. H.; Wen, H. C.; Lu, J. P.; Kwong, D. L. Dual Work Function Metal Gates using Full Nickel Silicidation of Doped Poly-Si. *IEEE Electron Device Lett.* **2003**, *24*, 631–633.

### **ACS Applied Materials & Interfaces**

(28) Bailey, R. S.; Kapoor, V. J. Variation in The Stoichiometry of Thin Silicon Nitride Insulating Films on Silicon and Its Correlation with Memory Traps. J. Vac. Sci. Technol. **1982**, 20, 484–487.

(29) Mishra, A.; Janardanan, A.; Khare, M.; Kalita, H.; Kottantharayil, A. Reduced Multilayer Graphene Oxide Floating Gate Flash Memory with Large Memory Window and Robust Retention Characteristics. *IEEE Electron Device Lett.* **2013**, *34*, 1136–1138.

(30) Stankovich, S.; Dikin, D. A.; Piner, R. D.; Kohlhaas, K. A.; Kleinhammes, A.; Jia, Y.; Wu, Y.; Nguyen, S. T.; Ruoff, R. S. Synthesis of Graphene-Based Nanosheets via Chemical Reduction of Exfoliated Graphite Oxide. *Carbon* **2007**, *45*, 1558–1565.

(31) Ulman, A. Formation and Structure of Self-Assembled Monolayers. *Chem. Rev.* **1996**, *96*, 1533–1554.

(32) Yang, H.; Li, F.; Shan, C.; Han, D.; Zhang, Q.; Niu, L.; Ivaska, A. Covalent Functionalization of Chemically Converted Graphene Sheets via Silane and Its Reinforcement. *J. Mater. Chem.* **2009**, *19*, 4632–4638.

(33) Ou, J.; Wang, Y.; Wang, J.; Liu, S.; Li, Z.; Yang, S. Self-Assembly of Octadecyltrichlorosilane on Graphene Oxide and the Tribological Performances of the Resultant Film. *J. Phys. Chem. C* **2011**, *115*, 10080–10086.

(34) Ganesh, V. A.; Dinachali, S. S.; Jayaraman, S.; Sridhar, R.; Raut, H. K.; Gora, A.; Baji, A.; Nair, A. S.; Ramakrishna, S. One-step Fabrication of Robust and Optically Transparent Slippery Coatings. *RSC Adv.* **2014**, *4*, 55263–55270.

(35) Seo, J. H.; Yang, R.; Brzezinski, J. Z.; Walker, B.; Bazan, G. C.; Nguyen, T.-Q. Electronic Properties at Gold/Conjugated-Polyelec-trolyte Interfaces. *Adv. Mater.* **2009**, *21*, 1006–1011.

(36) Braun, S.; Salaneck, W. R.; Fahlman, M. Energy-Level Alignment at Organic/Metal and Organic/Organic Interfaces. *Adv. Mater.* **2009**, *21*, 1450–1472.

(37) Kong, B.-S.; Geng, J.; Jung, H.-T. Layer-by-Layer Assembly of Graphene and Gold Nanoparticles by Vacuum Filtration and Spontaneous Reduction of Gold Ions. *Chem. Commun.* **2009**, 2174–2176.

(38) Yin, Z.; Wu, S.; Zhou, X.; Huang, X.; Zhang, Q.; Boey, F.; Zhang, H. Electrochemical Deposition of ZnO Nanorods on Transparent Reduced Graphene Oxide Electrodes for Hybrid Solar Cells. *Small* **2010**, *6*, 307–312.

(39) Han, S.-T.; Zhou, Y.; Yang, Q. D.; Zhou, L.; Huang, L.-B.; Yan, Y.; Lee, C.-S.; Roy, V. A. L. Energy-Band Engineering for Tunable Memory Characteristics through Controlled Doping of Reduced Graphene Oxide. *ACS Nano* **2014**, *8*, 1923–1931.

(40) Kim, J. S.; Park, J. H.; Lee, J. H.; Jo, J.; Kim, D.-Y.; Cho, K. Control of The Electrode Work Function and Active Layer Morphology via Surface Modification of Indium Tin Oxide for High Efficiency Organic Photovoltaics. *Appl. Phys. Lett.* **200**7, *91*, 112111.

(41) Yokota, K.; Takai, K.; Enoki, T. Carrier Control of Graphene Driven by the Proximity Effect of Functionalized Self-assembled Monolayers. *Nano Lett.* **2011**, *11*, 3669–3675.

(42) Misra, A.; Kalita, H.; Kottantharayil, A. Work Function Modulation and Thermal Stability of Reduced Graphene Oxide Gate Electrodes in MOS Devices. *ACS Appl. Mater. Interfaces* **2013**, *6*, 786– 794.

(43) Kim, S.-J.; Lee, J.-S. Flexible Organic Transistor Memory Devices. *Nano Lett.* **2010**, *10*, 2884–2890.

(44) Leong, W. L.; Mathews, N.; Tan, B.; Vaidyanathan, S.; Dotz, F.; Mhaisalkar, S. Towards Printable Organic Thin Film Transistor Based Flash Memory Devices. *J. Mater. Chem.* **2011**, *21*, 5203–5214.

(45) Zhou, Y.; Han, S.-T.; Xu, Z.-X.; Roy, V. A. L. The Strain and Thermal Induced Tunable Charging Phenomenon in Low Power Flexible Memory Arrays with a Gold Nanoparticle Monolayer. *Nanoscale* **2013**, *5*, 1972–1979.

(46) Raghunathan, S.; Krishnamohan, T.; Parat, K.; Saraswat, K. In Investigation of Ballistic Current in Scaled Floating-Gate NAND FLASH and a Solution. *Proc. IEEE Int. Electron Devices Meet.* **2009**, 819– 822.

(47) Blomme, P.; Cacciato, A.; Wellekens, D.; Breuil, L.; Rosmeulen, M.; Kar, G. S.; Locorotondo, S.; Vrancken, C.; Richard, O.; Debusschere, I.; Van Houdt, J. Hybrid Floating Gate Cell for Sub-20-

nm NAND Flash Memory Technology. *IEEE Electron Device Lett.* **2012**, 33, 333–335.